KATALOG IDT

|

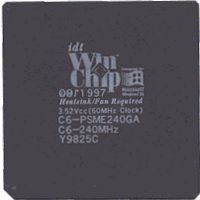

Procesor WinChip C6Jest pierwszym procesorem firmy IDT. Dostarcza dużej wydajności za niezwykle niską cenę. Jest przeznaczony dla rynku komputerów w cenie do 2000 złotych. Zawiera instrukcje MMX i jest dostępny z częstotliwościami taktowania 200, 225 i 240 MHz. |

|

| Ogólnie o produkcie Szczegóły techniczne Podsumowanie | ||

Procesor WinChip C6. Częstotliwość taktowania: 200, 225, 240 MHz; częstotliwość

magistrali: 66 i 75 MHz; zasilanie pojedyncze: 3.3 lub 3.52 V; złącze: Socket

7; cache: L1 64 kB, L2 brak; technologia MMX dla obsługi multimediów.

|

||

|

|

||

|

|

||

WinChip C6 - prostota i dobra wydajność za wyjątkową cenę.

Niezwykle małe rozmiaryW czasach super- i hiperskalarnych procesorów, architektura WinChipa poraża swoją prostotą. Struktura ma niewielkie wymiary - 88 milimetrów kwadratowych, przy niewyrafinowanej technologii 0,35 mikrometra 4-warstwowej CMOS! Jest to główny czynnik kształtujący niezwykle niską cenę układu scalonego; WinChip jest znacząco mniejszy od swoich konkurentów, a więc i tańszy. Wielkość układu wpływa także na bardzo mały pobór mocy, a więc na mniejsze wydzielanie energii cieplnej przez układ - wymaga tylko bardzo prostych układów chłodzących.

Architektura

Sercem procesora, przystosowanego do osadzenia w gnieździe Socket 7, jest bardzo jednostka RISC z pojedynczą, niedługą (4-pozycyjną) kolejką rozkazów, bez zwielokrotnionych rejestrów, mechanizmów predykcji skoków i innych powikłań, które traktujemy jako niezbędny element we współczesnych konstrukcjach. Innowacją jest tutaj wczesne rozdzielenie danych i rozkazów, następujące już na poziomie ich pobrania - procesor jest wyposażony w osobne pamięci cache dla instrukcji i dla danych. Pobranie instrukcji następuje poprzez bufor TLB współpracujący z pamięcią cache drugiego poziomu. Bufor ten zapewnia znaczące zwiększenie "poziomu trafień" zarówno cache L2, jak i cache instrukcji. Współpraca dwudrogowego mechanizmu skojarzeniowego cache L1 z czterodrogowym skojarzeniowym buforem TLB to prawie dwukrotne zmniejszenie poziomu "chybień" L1.

Pamięć podręczna i translator

Procesor posiada wbudowaną pamięć podręczną L1 o pojemności 64 kB (32

kB pamięci podręcznej dla rozkazów i 32 kB pamięci podręcznej dla danych.

Z pamięci podręcznej instrukcje są pobierane do translatora x86 na kod

RISC stanowiącego newralgiczny element procesora. Translator tłumaczy na

pojedyncze instrukcje wewnętrznego kodu RISC te rozkazy x86, które można

wykonać w pojedynczym cyklu. Pozostałe realizowane są jako sekwencje mikroprogramowe,

podobnie jak w klasycznych procesorach CISC. Na szczęście takich instrukcji

jest stosunkowo niewiele i w typowych kodach programów występują one dość

rzadko. Instrukcje RISC powstałe w translatorze przekazywane są, poprzez

czteropozycyjną kolejkę, do jednostki wykonawczej. Bardzo krótka kolejka

to ustępstwo na rzecz rezygnacji z predykcji skoków; utrata trzech cykli

oczekujących w kolejce w wyniku wykonania instrukcji skoku warunkowego

nie jest wielką stratą - przy długich, kilkunastocyklowych kolejkach, bez

predykcji skoków straty mogłyby być większe, niż zysk wynikający z zastosowania

kolejek. Oczekujące w kolejce instrukcje są w kolejnych fazach dekodowane,

adresowane, wykonywane i zapisywane w postaci wyników. Jednostka wykonawcza

WinChipa to aż trzy równoległe jednostki - stałoprzecinkowa ALU, procesor

zmiennoprzecinkowy oraz macierzowy procesor MMX. Dane dla operacji, jak

również końcowe wyniki, przekazywane są do pamięci RAM za pośrednictwem

pamięci podręcznej cache. Pomiędzy pamięciami cache a zewnętrzną szyną

procesora zastosowano 4 rejestry buforowe (64-bitowe), które zapewniają

kolejne zwiększenie płynności przepływu danych.

Niezwykła plynność przepływu danych

Konstruktorzy WinChipa postawili przede wszystkim na płynność przepływu

danych, zapewnianą przez bardzo sprawny system pamięci podręcznych; mimo

niedługiej kolejki rozkazów, nie pozostawili też całkowicie na los szczęścia

zagadnienia skoków i powrotów - zrezygnowali ze złożonej i kosztownej logiki

predykcji skoków, ale równocześnie wyposażyli procesor w 8-poziomowy sprzętowy

stos skoków i powrotów, gwarantujący znaczące usprawnienie obsługi przerwań.

Całość sprawia wrażenie optymalnego kompromisu pomiędzy technologią RISC

a chaotyczną struktura kodu x86 - wydają się to potwierdzać wyniki przeprowadzonych

testów.

Zasilanie tylko pojedynczym napięciem

WinChip ma jeszcze jedną zaletę - będąc przystosowanym do zasilania

pojedynczym napięciem 3.3 lub 3.52 V oraz będąc przystosowanym do złącza

Socket 7, stanowi propozycję procesora wyposażonego w rozszerzenie MMX

dla wszystkich posiadaczy starszych płyt głównych z pojedynczym napięciem

zasilającym procesor (konstrukcje dla procesora P54 - Intel Pentium bez

funkcji MMX).

Kompatybilność

WinChip jest kompatybilny ze wszystkimi systemami operacyjnymi dla

procesorów x86, a więc DOS, Windows 3.1, Windows 95, Windows 98, Windows

NT, OS/2, Linux i wielu innymi. Współpracuje z płytami głównymi wyposażonymi

w chipsety firm Intel, ALi, SiS, Via i biosy firm Award, Phoenix i AMI.

Spełnia także wymogi kompatybilności z rokiem 2000.

Dane techniczne procesora WinChip C6

ArchitekturaProcesor RISC.

Proces technologiczny

0.35 mikrona. 4-warstwowy CMOS.

Rozmiar Die

88 mm2.

Częstotliwość taktowania

200, 225, 240 MHz.

Częstotliwość magistrali

66 i 75 MHz (dla wersji z częstotliwościa taktowania 225 MHz).

Pamięć podręczna

Dwupoziomowa. L1: 64 kB (32 kB cache danych i 32 KB cache instrukcji); L2: obsługa pamięci zewnętrznej na płycie głównej.

Koprocesor

Wbudowany, zgodny ze standardem IEEE-754, wykonujący także operacje 80-bitowe.

Multimedia

Technologia MMX (rejestry automatycznie wyłączane, gdy nie są używane).

Cechy dodatkowe

Bufor danych TLB, 8-poziomowy sprzętowy stos skoków i powrotów.

Obudowa

CPGA.

Złącze

Socket 7.

Napięcia zasilające

Pojedyncze: 3.3 lub 3.52 V.

Kompatybilność sprzętowa

Kompatybilny z procesorami rodziny X86.

Kompatybilność programowa

DOS, Windows 3.1x, Windows 95, Windows 98,Windows NT 4.0, OS/2, Linux.

Temperatura pracy

od 0 do 65 st. C.

Gwarancja 1 rok

Windows jest znakiem handlowym Microsoft Corp. Wszystkie inne znaki firmowe i nazwy produktów są znakami handlowymi lub zastrzeżonymi znakami handlowymi odpowiednich firm. Specyfikacje przedstawione w tym dokumencie mogą bez uprzedzenia ulec zmianie. Emblemat Energy Star nie oznacza wyróżnienia przez EPA żadnej konkretnej firmy ani produktu.